AN11817 BGA3131 DOCSIS 3.1 upstream amplifier Rev. 1 – 24 May 2016

**Application note**

#### **Document information**

| Info                | Content                                                                                                                                             |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords            | BGA3131, Evaluation board, DOCSIS 3.1                                                                                                               |

| Abstract            | This application note provides circuit schematic, PCB layout, BOM and typical EVB performance of the <i>BGA3131 DOCSIS 3.1 upstream amplifier</i> . |

| Ordering info       | <u>Evaluation kit number:</u> OM17024<br>12NC: 9340 703 22598                                                                                       |

| Contact information | For more information, please visit: <u>http://www.nxp.com</u>                                                                                       |

#### **Revision history**

## **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

AN11817

Application note

All information provided in this document is subject to legal disclaimers.

Rev. 1 — 24 May 2016

### 1. Introduction

The BGA3131 is an upstream amplifier meeting the Data Over Cable Service Interface Specifications 3.1. It is designed for cable modems, CATV set top box and VoIP modem applications.

It amplifies the modulated signals coming from the SoC to a defined power level at the F-connector towards the network.

The device can handle signals between 5 MHz to 205 MHz. The BGA3131 provides 58 dB gain control range in 1 dB increments with high incremental accuracy. Its maximum gain setting delivers 37 dB voltage gain and a superior linear performance.

It supports the DOCSIS 3.1 output power levels of 68dBmV (RMS) while meeting the stringent ACLR requirements.

The current consumption and gain settings are controlled through a digital serial interface (SPI)

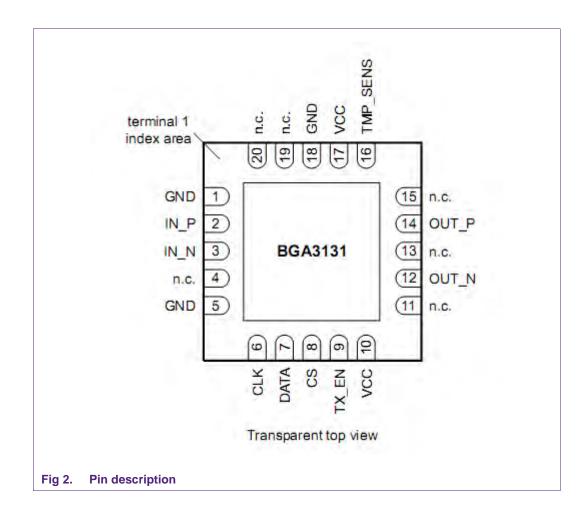

The BGA3131 is housed in 20 pins 5 mm x 5 mm leadless HVQFN package and don't need additional heatsink.

## 2. Product description

The BGA3131 operates at 5 V supply. The gain is controlled via 3-wire SPI-interface.

The current consumption can be reduced in 4 steps via the serial interface. This interface enables the user to optimize between DC power efficiency and linearity. In addition, the current is automatically reduced at lower gain settings while preserving the linearity performance. In disable mode, the device draws typically 25 mA while it can be still programmed to new gain and current settings.

BGA3131 key features and benefits:

- Low Power consumption of 3.3 W (typical) at highest current and gain setting

- 58 dB gain control range in 1 dB steps using a 3-wire serial interface

- 5 MHz to 205 MHz frequency operating range

- ± 0.4 dB incremental gain step accuracy

- Maximum voltage gain 37 dB

- Excellent IMD3 of -60 dBc at 68 dBmV total output power

- Excellent second harmonic level of -60 dBc at 68 dBmV total output power

- Excellent third harmonic level of -60 dBc at 68 dBmV total output power

- Excellent noise figure of 6.5 dB at maximum gain

- Capable of transmitting modulated carriers while meeting the DOCSIS 3.1 ACLR specification. At an output power of 65dBmV at the F-connector (assuming 3 dB of output loss), the typical ACLR is-64 dBc

- 5 V single supply operation

- Excellent ESD protection at all pins

- Unconditionally stable

- Compliant to Directive 2002/95/EC, regarding Restriction of Hazardous Substances

- (RoHS)

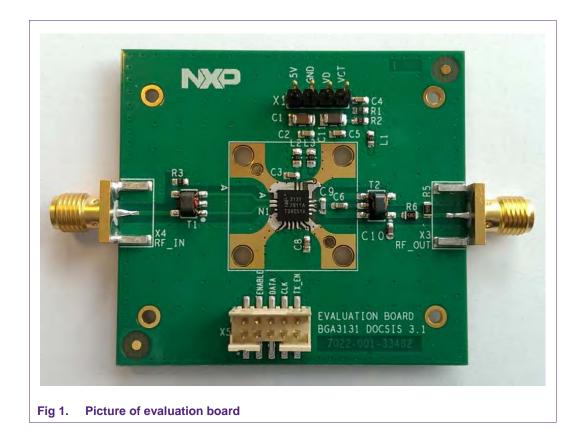

## 3. BGA3131 DOCSIS 3.1 upstream amplifier evaluation board

The BGA3131 customer evaluation kit enables the user to evaluate the RF performance of the DOCSIS 3.1 upstream amplifier. The kit comes with a USB-interface board and customer software which allows you to use your PC to control the SPI interface of the BGA3131. You can set the gain state and advanced features as current consumption and power down of the BGA3131. The board is supplied with two SMA connectors to connect input and output to the RF test equipment in 50  $\Omega$  test system.

The Customer evaluation kit (OM17024) contains fully populated BGA3131 RF evaluation board, USB interface board, flat cable, USB flash driver (containing evaluation software, introduction,...)

The plug & play control software doesn't require additional driver for installation.

### 3.1 Application circuit and component selection

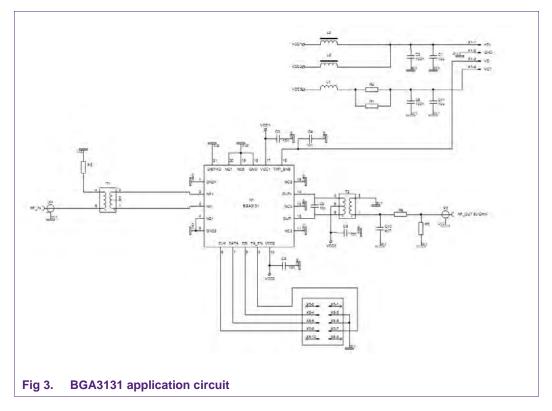

The application board circuit diagram that is implemented on the EVB is shown in Fig 3

It's important that the BGA3131 use a common supply voltage to avoid delays between the different supply pins of the BGA3131.

No bias inductors needed (if needed ferrite beads or inductors can be used to reduce the noise on VCC). Keep the supply decoupling capacitors close by the VCC pins.

For measurements in a 50  $\Omega$  system R5 and R6 at RF-output, a 1:4 transformer at RF-input are added for impedance transformation from 75  $\Omega$  to 50  $\Omega$ . These are not required in the final application.

In the final application the balanced output (37.5  $\Omega$  differential) of the BGA3131 needs to be matched to a single-ended 75  $\Omega$  load using a 1:2 ratio transformer.

The output transformer (1:2) ratio is needed on the final application, MACOM MABA-011056 or Murata #617PT-2291=P3 can be used.

The transformer also cancels even mode distortion products and common mode signals, such as the voltage transients that occur while enabling and disabling the amplifiers.

BGA3131 pin 13 isn't used and also not internal connected, it can be left open, grounded or connected to VCC.

It's advised to place 2 additional matching capacitors C9 (10pF) and C10 (4.7pF) for optimal RF performance.

Control line:

The maximum clock frequency is 25 MHz and the maximum load on Data line is 30 pF.

### 3.2 PCB layout information

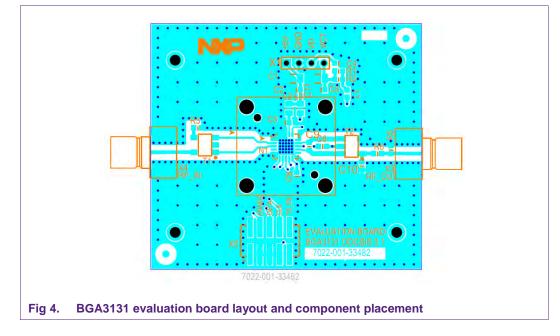

The supply decoupling capacitors are placed close to the supply pins.

Combine all the BGA3131 supply voltages on one common 5V supply to avoid delays between the supply pins!

The evaluation board uses grounded micro strip lines using different impedances for input and output lines.

Consider the losses of the used transformers and 5.7dB for the output matching resistors (R5 & R6) for deembedding.

Use thermal vias (25 cu filled vias recommended) below the BGA313, for better heatsink keep the areas (as huge as possible) on all layers below the BGA3131 with cupper.

For more info see application note AN11753 "Thermal considerations BGA3131".

The layout and component placement of the BGA3131 evaluation board is given in Fig 4

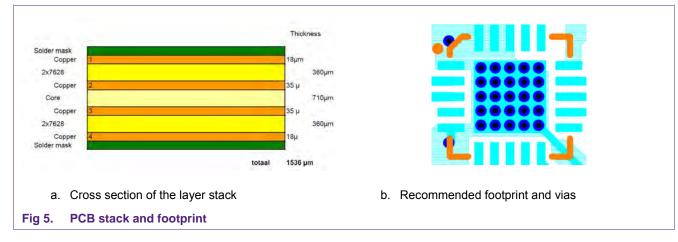

### 3.3 PCB stack and recommended footprint

The used PCB material is 4 layer FR4 printed circuit board, total height of the pcb is roughly 1.5mm.

The reason for the chosen pcb stack is to have robust and good thermal behavior evaluation board.

The first layer is for RF routing + signal, second layer is for RF ground + heat sink, third layer is for signal line + heat sink and the fourth layer is again ground + heat sink.

For thermal reasons it's recommended to have 25 cu filled ground via holes of 0.3 mm as shown in Fig 5b.

### 3.4 Bill of materials

Table 1 gives the bill of materials as is used on the EVB.

#### Table 1. Bill of materials of evaluation board in Fig. 4

| Designator    | Description                  | Footprint | Value  | Supplier Name/type | Comment/function                                                   |

|---------------|------------------------------|-----------|--------|--------------------|--------------------------------------------------------------------|

| N1            | BGA3131                      | HVQFN20   |        | NXP BGA3131        | DOCSIS 3.1 upstream amplifier                                      |

| C1, C11       | capacitor                    | 1206      | 10 uF  | Various            | Decoupling                                                         |

| C2, C5        | capacitor                    | 0603      | 100 nF | Murata GRM1555     | Decoupling                                                         |

| C3, C4,C6, C8 | capacitor                    | 0603      | 10 nF  | Murata GRM1555     | Decoupling                                                         |

| C9            | capacitor                    | 0603      | 10 pF  | Murata GRM1555     | Matching                                                           |

| C10           | capacitor                    | 0603      | 4.7 pF | Murata GRM1555     | Matching                                                           |

| L1, L2, L3    | place holder<br>for inductor | 0603      | 0 Ω    | Various            | Place holder for optional inductor 0 $\Omega$ mounted              |

| R1, R2, R3    | resistor                     | 0603      | 0Ω     | Various            |                                                                    |

| R5            | resistor                     | 0603      | 86.6 Ω | Various            | 75 $\Omega$ to 50 $\Omega$ conversion for measurement purpose only |

| R6            | resistor                     | 0603      | 43.2 Ω | Various            |                                                                    |

| T1            | transformer                  | -         | -      | TOKO: #617PT-1664  | Input matching 1:4 (50 $\Omega$ to 200 $\Omega)$                   |

|               |                              |           |        |                    |                                                                    |

**Application note**

All information provided in this document is subject to legal disclaimers.

| Designator | Description      | Footprint | Value | Supplier Name/type     | Comment/function                                   |

|------------|------------------|-----------|-------|------------------------|----------------------------------------------------|

| T2         | transformer      | -         | -     | MACOM: MABA-<br>011056 | Output matching 1:2 (37.5 $\Omega$ to 75 $\Omega)$ |

| X1         | Header, 4P       | -         | -     | -                      | DC connections                                     |

| X3, X4     | SMA<br>connector | -         | -     | -                      | RF connections                                     |

| X5         | Header, 10P      | -         | -     | -                      | Control interface (USB to SPI)                     |

### 3.5 Summary of application / design information

- Use common supply voltage to avoid supply voltage delays between the BGA3131 supply pins

- No need on bias inductors. Ferrite beads or inductors can be used to reduce the noise on supply voltage (take care on routing, less coupling to RF-out, avoid ground loop)

- Place the supply decoupling capacitors close to the VCC pins of the BGA3131, propose to add additional to the 10 nF decoupling capacitor on the VCC pins another 10 uF to reduce distortions or noise coming from the supply.

- The output transformer 1:2 (37.5 Ω differential to 75 Ω single-ended) should cover the DOCSIS 3.1 bandwidth (5 – 205 MHz), examples are MACOM MABA-011056 or Murata #617PT-2291=P3

- For optimal RF-performance (output matching) it's recommended to add C9 (10 pF) and C10 (4.7 pF) at RF-out.

- Pin 13 isn't used (not internal connected), it can be left open, grounded or connected to VCC

- Input transformer 1:4 (200  $\Omega$  differential to 50  $\Omega$  single-ended), R5 and R6 (75  $\Omega$  to 50  $\Omega$ ) at RF-out are only used for measurement purpose on the application board to have 50  $\Omega$  at the RF-in and RF-out sma-connector and not required on the final application

- Use thermal vias (25 cu filled vias recommended) below the BGA3131, for better heatsink keep the ground areas (as huge as possible) on all layers below the BGA3131 with cupper

4.

# BGA3131 evaluation board connections and control software

The BGA3131 evaluation board can be controlled via the control software and doesn't need any driver for Windows PC's.

Before starting with the evaluation following steps needs to be done:

- 1. Connect the interface board to the BGA3131 evaluation board (X5) using the flat cable.

- 2. Power the BGA3131 evaluation board with 5V at pin +5V and VCT (connect both supply pins on same 5V supply to avoid delays on the supply pins). Use a 5W power supply.

- 3. Insert the interface board in a free USB slot on PC.

- 4. Insert the USB flash driver in another free USB slot on the PC.

- 5. Launch the customer software BGA3131\_XX by double click on the icon.

- 6. Now the GUI (shown in Fig 6) will appear to control the gain, current and the TX\_Enable function of the BGA3131.

| TX_Enable | Current                                           | Typical Gain                    |

|-----------|---------------------------------------------------|---------------------------------|

|           | <ul> <li>CS1</li> <li>CS2</li> <li>CS3</li> </ul> | 0 63<br>63<br>39 dB -1 dB +1 dB |

|           | -                                                 | USB not connected DevId:        |

Gain can be set by using the slider, +/- buttons or entered (maximum gain is at setting 63).

TX can be enabled and disabled by using the TX\_Enable button (typical current is 25 mA in disable mode)

Current can be set via the CS0...CS3 (see Fig 7)

| Current setting | Typical supply current (mA) |

|-----------------|-----------------------------|

| CS0             | 350                         |

| CS1             | 410                         |

| CS2             | 480                         |

| CS3             | 660                         |

## 5. Measurement results

### 5.1 Static characteristics

Typical values at VCC = 5 V; current setting = 3; gain setting 50 up and including 63; T<sub>case</sub> = 25  $^{\circ}$ C; Zi(dif) = 200  $\Omega$ ; Zo(se) = 75  $\Omega$ ; unless otherwise specified.

| Symbol          | Parameter                | Conditions                         | Min  | Тур | Max                   | Uni |

|-----------------|--------------------------|------------------------------------|------|-----|-----------------------|-----|

| V <sub>cc</sub> | supply voltage           |                                    | 4.75 | 5.0 | 5.25                  | V   |

| lcc             | supply current           | transmit-enable mode; TX_EN = HIGH | 610  | 660 | 720                   | mA  |

|                 |                          | transmit-disable mode; TX_EN = LOW | -    | 25  | -                     | mΑ  |

| VIH             | HIGH-level input voltage | <u>ញ</u>                           | 1.8  | -   | V <sub>CC</sub> + 0.6 | V   |

| VIL             | LOW-level input voltage  | <u>ញ</u>                           | 0    | -   | 0.8                   | V   |

| Р               | power dissipation        |                                    | -    | 3.3 |                       | W   |

[1] Voltage on the control pins.

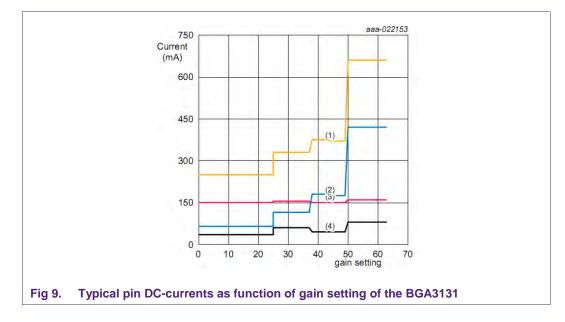

- VCC = 5 V; current setting = 3; Tamb = 25  $^{\circ}$ C;

- (1) total current;  $I_{CC1} + I_{CC2} + ICT$

- (2) ICT; output balun center tap current

- (3) I<sub>CC1</sub>; current through Pin #17 (V<sub>CC1</sub>)

- (4) I<sub>CC2</sub>; current through Pin #16 (V<sub>CC2</sub>)

### 5.2 ACLR characteristics

Typical values at VCC = 5 V; current setting = 3; Gain setting 60;  $T_{case} = 25 \ ^{\circ}C$ ;  $Zi_{(dif)} = 200 \ \Omega$ ;  $Zo_{(se)} = 75 \ \Omega$ ; channel bandwidth = 192 MHz; integration bandwidth = 9.6 MHz; f = 5 MHz to 205 MHz; unless otherwise specified.

| Symbol | Parameter                   | Conditions                                                                                                                                                     | Min | Тур | Max | Unit |

|--------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| DOCSIS | 3.1                         |                                                                                                                                                                | _   |     |     |      |

| ACLR   | LR adjacent channel leakage | P <sub>i</sub> = 34 dBmV(rms); P <sub>L</sub> = 68 dBmV(rms)                                                                                                   |     |     |     |      |

|        | ratio                       | channel configuration: channel bandwidth is<br>192 MHz, with exclusion band at 147.5 MHz, with a<br>bandwidth of 9.6 MHz. Input signal with a PAPR<br>of 13 dB | -   | -64 | -58 | dBc  |

Fig 10. Typical ACLR characteristics of the BGA3131 evaluation board

AN11817

### 5.3 Dynamic characteristics

The table below shows the typical values at VCC = 5 V; current setting = 3; gain setting 15 up and including 63;  $T_{case} = 25 \,^{\circ}C$ ;  $Z_{i(dif)} = 200 \,\Omega; Z_{0(se)} = 75 \,\Omega$ ; voltage gain does include loss due to output transformer; unless otherwise specified. All RF parameters are measured on an application board with the circuit as shown in Fig.3 and components implemented as listed in Table 1.

| Symbol                              | Parameter                                           | Conditions                                                                                                                           |        | Min | Тур   | Max | Unit |

|-------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------|-----|------|

| Gv                                  | voltage gain                                        | gain code = 111111                                                                                                                   | [1][2] | -   | 37    | -   | dB   |

|                                     |                                                     | gain code = 001111                                                                                                                   | [1][2] | -   | -11   | -   | dB   |

| G <sub>flat</sub>                   | gain flatness                                       | f = 5 MHz to 205 MHz                                                                                                                 | [1]    | -   | ± 0.5 | -   | dB   |

| RLout                               | output return loss                                  | transmit mode enable over all gain settings, measured in 75 $\Omega$ system                                                          |        | -   | 14    | -   | dB   |

|                                     |                                                     | transmit mode disable over all gain settings, measured in 75 $\Omega$ system                                                         |        | -   | 12    | -   | dB   |

| RL <sub>in</sub>                    | input return loss                                   | transmit mode enable overall gain settings, measured in 200 $\Omega$ system                                                          |        | -   | 20    | -   | dB   |

|                                     |                                                     | transmit modes disable overall gain settings, measured in 200 $\Omega$ system                                                        |        | -   | 20    | -   | dB   |

| G <sub>step</sub>                   | gain step                                           |                                                                                                                                      | [1]    | -   | 1.0   | -   | dB   |

| EG(dif)                             | differential gain error                             |                                                                                                                                      | [1]    | -   | ± 0.4 | -   | dB   |

| R <sub>i(dif)</sub>                 | differential input resistance                       |                                                                                                                                      |        | -   | 200   | -   | Ω    |

| R <sub>o(dif)</sub>                 | differential output resistance                      |                                                                                                                                      |        | -   | 37.5  | -   | Ω    |

| frange                              | frequency range                                     |                                                                                                                                      |        | 5   | -     | 205 | MHz  |

| aisol                               | isolation                                           | transmit-disable mode; TX_EN = LOW;<br>f = 205 MHz                                                                                   |        | -   | 60    | -   | dB   |

| NF                                  | F noise figure                                      | transmit mode; gain code = 111111                                                                                                    |        | -   | 6.5   | -   | dB   |

|                                     |                                                     | transmit mode; gain code = 100110                                                                                                    |        | -   | 15    | -   | dB   |

| t <sub>sw(G)</sub> gain switch time | transmit-disable/transmit-enable transient duration |                                                                                                                                      | -      | 3.0 | -     | μs  |      |

|                                     |                                                     | transmit-enable/transmit-disable transient duration                                                                                  |        | -   | 0.5   | -   | μs   |

| V <sub>trt</sub>                    | transient voltage                                   | transmit-disable/transmit-enable transient step size; peak value                                                                     |        |     |       |     |      |

|                                     |                                                     | ≥ 58 dBmV output power                                                                                                               | [3][4] | -   | 45    | -   | mV   |

|                                     |                                                     | 52 dBmV output power                                                                                                                 | [3][4] | -   | 15    | -   | mV   |

|                                     |                                                     | 46 dBmV output power                                                                                                                 | [3][4] | -   | 10    | -   | mV   |

|                                     |                                                     | 40 dBmV output power                                                                                                                 | [3][4] | -   | 5     | -   | mV   |

|                                     |                                                     | ≤ 34 dBmV output power                                                                                                               | [3][4] | -   | 3     | -   | mV   |

| α <sub>2H</sub>                     | second harmonic level                               | transmit-enable mode; gain code = 111111;<br>P <sub>i</sub> = 31.0 dBmV(rms); P <sub>L</sub> = 68.0 dBmV(rms) into<br>75 Ω impedance |        | -   | -65   | -   | dBc  |

| α <sub>3H</sub>                     | third harmonic level                                |                                                                                                                                      |        | -   | -65   | -   | dBc  |

| IMD3                                | third-order intermodulation distortion              | transmit-enable mode; gain code = 111111;<br>P <sub>L</sub> = 65 dBmV(rms) per tone into<br>75 Ω impedance                           |        | -   | -60   | -   | dBc  |

| PL(1dB)                             | output power at 1 dB gain compression               | CW input signal RMS value; frequency = 205MHz                                                                                        |        | -   | 78    | -   | dBm  |

### Fig 11. Typical performance of the BGA3131 evaluation board

[1] Pi ≤ 30 dBmV.

[2] Excluding loss of resistive matching circuit, to match 75  $\Omega$  to 50  $\Omega.$

- [3] Measured at the output of the output balun.

- [4] Assume 3 dB loss between by output of the balun and F-connector in the final application.

### 5.4 Measurement set-up

For accurate P1dB, IP3 and harmonic measurements (improve the dynamic range of the measurement setup) add bandpass- or low pass-filter on the signal generator. Filters need good broad band matching to meet their specified filter characteristics, therefore add minimum 3 dB attenuator at bandpass or low pass filter output to have proper filtering!

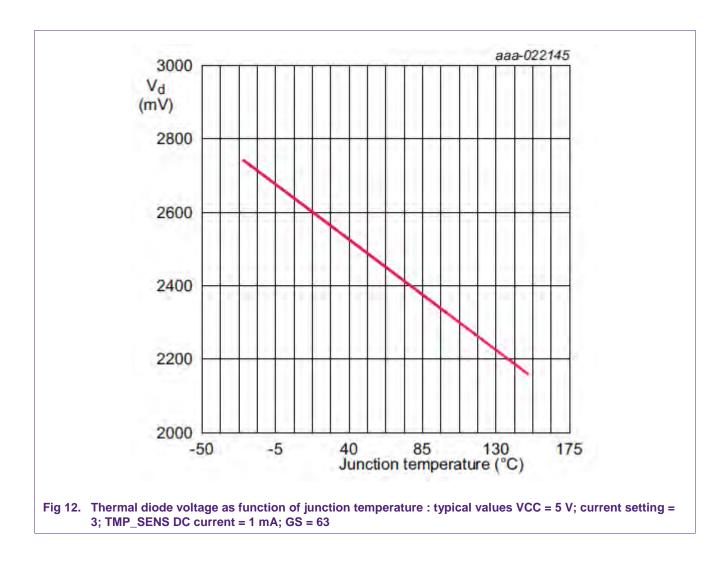

### 6. Temperature sense using build in temperature diode

The build in temperature diode can be used to measure the junction temperature of the BGA3131 by feeding 1 mA constant current at pin 16 and measuring the voltage at pin 16.

AN11817

## 7. Customer Evaluation Kit

The customer evaluation kit contains:

- BGA3131 evaluation board

- Interface board (USB to SPI)

- Flat cable

- 5 loose samples of the BGA3131

- USB flash driver (contains control software, introduction)

AN11817

## 8. Abbreviations

| Table 2. | Abbreviations                               |

|----------|---------------------------------------------|

| Acronym  | Description                                 |

| AC       | Alternating Current                         |

| DC       | Direct Current                              |

| RMS      | Root Mean Square                            |

| ESD      | Electro Static Discharge                    |

| HVQFN    | Heat sink Very thin Quad Flat pack No leads |

| PCB      | Printed Circuit Board                       |

| RF       | Radio Frequency                             |

| SMD      | Surface Mounted Device                      |

| CATV     | Community Antenna Television                |

| CW       | Continuous Wave                             |

| OFDM     | Orthogonal Frequency Division Multiplexing  |

| PAPR     | Peak-to-Average Power Ratio                 |

| SMA      | Sub-Miniature version A                     |

| ТΧ       | Transmission                                |

| SoC      | System on a Chip                            |

| VoIP     | Voice over Internet Protocol                |

AN11817

## 9. Legal information

### 9.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 9.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP

Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

### 9.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

# 10. List of figures

| Fig 1.  | Picture of evaluation board3                                                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig 2.  | Pin description5                                                                                                                                          |

| Fig 3.  | BGA3131 application circuit6                                                                                                                              |

| Fig 4.  | BGA3131 evaluation board layout and                                                                                                                       |

|         | component placement7                                                                                                                                      |

| Fig 5.  | PCB stack and footprint8                                                                                                                                  |

| Fig 6.  | BGA3131 GUI control software10                                                                                                                            |

| Fig 7.  | BGA3131 GUI current setting11                                                                                                                             |

| Fig 8.  | Typical static characteristics of the BGA3131                                                                                                             |

|         | evaluation board11                                                                                                                                        |

| Fig 9.  | Typical pin DC-currents as function of gain setting of the BGA313112                                                                                      |

| Fig 10. | Typical ACLR characteristics of the BGA3131 evaluation board12                                                                                            |

| Fig 11. | Typical performance of the BGA3131 evaluation board13                                                                                                     |

| Fig 12. | Thermal diode voltage as function of junction<br>temperature : typical values VCC = 5 V; current<br>setting = 3; TMP_SENS DC current = 1 mA; GS<br>= 6314 |

| Fig 13. | Customer evaluation KIT15                                                                                                                                 |

**Application note**

## 11. List of tables

| Table 1. | Bill of materials of evaluation board in Fig. 48 |

|----------|--------------------------------------------------|

| Table 1. | Bill of materials of evaluation board in Fig. 48 |

Table 2. Abbreviations ......16

**Application note**

## 12. Contents

| 1.  | Introduction3                                |

|-----|----------------------------------------------|

| 2.  | Product description4                         |

| 3.  | BGA3131 DOCSIS 3.1 upstream amplifier        |

|     | evaluation board6                            |

| 3.1 | Application circuit and component selection6 |

| 3.2 | PCB layout information7                      |

| 3.3 | PCB stack and recommended footprint8         |

| 3.4 | Bill of materials8                           |

| 3.5 | Summary of application / design information9 |

| 4.  | BGA3131 evaluation board connections and     |

|     | control software10                           |

| 5.  | Measurement results11                        |

| 5.1 | Static characteristics11                     |

| 5.2 | ACLR characteristics12                       |

| 5.3 | Dynamic characteristics13                    |

| 5.4 | Measurement set-up14                         |

| 6.  | Temperature sense using build in temperature |

|     | diode14                                      |

| 7.  | Customer Evaluation Kit15                    |

| 8.  | Abbreviations16                              |

| 9.  | Legal information17                          |

| 9.1 | Definitions17                                |

| 9.2 | Disclaimers17                                |

| 9.3 | Trademarks17                                 |

| 10. | List of figures18                            |

| 11. | List of tables19                             |

| 12. | Contents20                                   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

#### © NXP B.V. 2016.

#### All rights reserved.

For more information, visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 24 May 2016 Document identifier: AN11817